The simulations for the proposed designs are verified using ISim Simulator. The power consumption is estimated using XPower Analyzer for a clock frequency of 10 MHz.

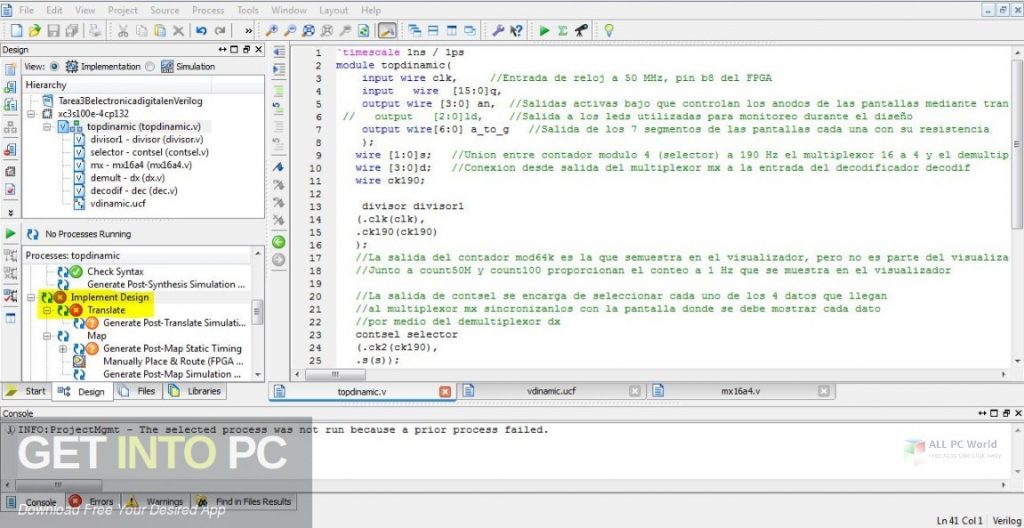

The area footprint is estimated in terms of the slices, flip flops and LUTs. The synthesis and implementation of the proposed architectures are performed using Verilog HDL in Xilinx ISE Design Suite 14.6. The results are evaluated for Xilinx FPGA platforms like Spartan 3, Virtex 4 and Virtex 6. For this tutorial, a smaller xc7k70t design is used, and the number of designs open at one time is limited. Hardware Requirements Xilinx recommends a minimum of 2 GB of RAM when using the PlanAhead tool on larger devices.

XILINX ISE 14.6 LICENSE SERIAL

This comprises a serial architecture and a reduced datapath architecture which are designed specifically for reduced area and low-power applications while choosing trade-offs from latency and performance. For installation instructions and information, see the ISE Design Suite 14: Release Notes, Installation, and Licensing (UG631). In this paper, two hardware architectures ideal for low-area footprint and low power are proposed. PICO is one of the lightweight SPN ciphers suitable for low-area and low-power applications. A universal CORDIC algorithm is now specified. Logic synthesis scripts updated for Xilinx ISE/XST 14.6. Documentation updated to RestructuredText. A single cycle is now needed per iteration. Among the ISE revisions, release 14.2 and later is recommended. For Kintex-7 and Virtex-7 with Gen2 interface (485T and non-XT/HT), Vivado 2014.1 and later is the preferred tool. For Spartan-6 and Virtex-6, Xilinx ISE 13.2 and later. The algorithms in this domain target moderate security while satisfying the constraints set for a desired application. Updated file organization for Github changed README to README.rst CORDIC-EULA.txt to LICENSE. When targeting Virtex-5 FPGAs, release Xilinx ISE 13.1 is preferred, see para-graph4.3.5. The rise in ubiquitous computing connecting resource-constrained devices had led to the emergence of a sub-domain in cryptography called lightweight cryptography.